- 您现在的位置:买卖IC网 > Sheet目录1210 > DK-SI-4S100G2N (Altera)KIT DEV STRATIX IV TRANSCEIVER

�� �

�

�

�6–4�

�Chapter� 6:� Stratix� IV� GT� Transceiver� Signal� Integrity� Demonstration�

�Running� the� Demonstration� Application� and� Test� Designs�

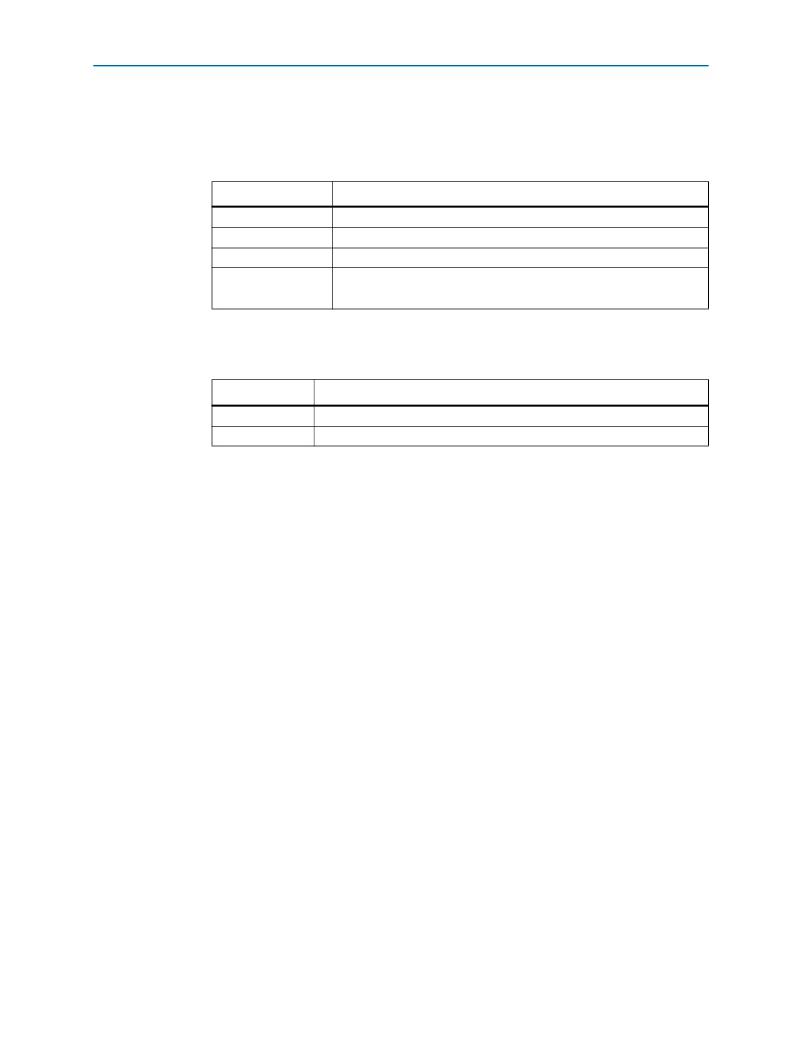

�Analog� Settings�

�You� can� use� the� application� to� dynamically� control� transceiver� PMA� settings� for� the�

�different� transceiver� blocks.� The� following� list� defines� the� analog� setting� parameters�

�in� the� control� panel� window:�

�Parameter�

�VOD�

�EQ�

�Gain�

�PE�

�Description�

�differential� output� driver� voltage.�

�equalization.�

�DC� gain.�

�preemphasis/deemphasis.�

�pre� ,� 1stpost� ,� and� 2ndpost� settings� represent� different� taps.�

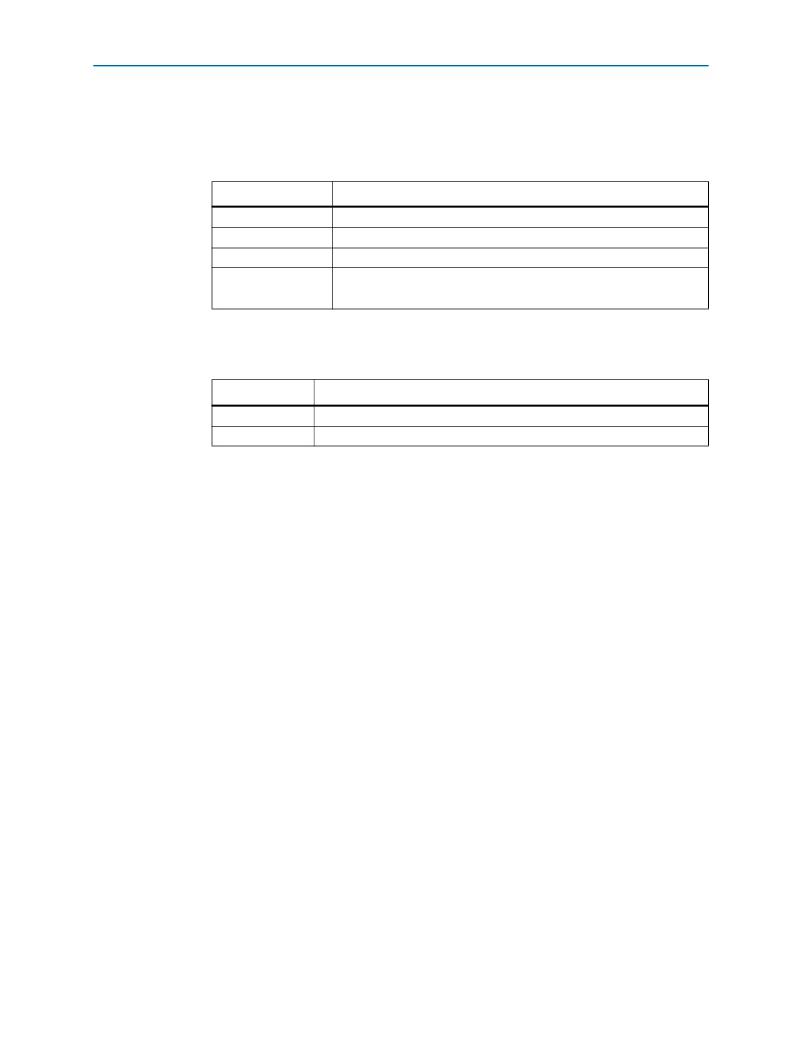

�Resets�

�The� following� list� describes� the� available� resets:�

�Reset�

�System�

�Error�

�Description�

�Reset� for� the� transceiver.�

�Reset� for� all� the� error� counters� to� zero.�

�1�

�After� the� System� Reset� is� asserted,� the� DataChk� Status� may� show� unsynced� for� some�

�channels� due� to� the� asynchronous� nature� of� the� reset.� Asserting� the� Data� Patrst�

�synchronizes� the� error� checker� to� the� transmitted� data.�

�Help�

�The� Help� button� displays� the� image� of� the� Stratix� IV� signal� integrity� board� and� also�

�highlights� the� channel� locations� and� their� data� rates� based� on� the� .sof� loaded.�

�Power� Down�

�Turn� on� Powerdown� to� power� down� the� transceiver� block.�

�Serial� Loopback�

�Serial� loopback� is� available� for� all� the� channels� and� can� be� controlled� during� run� time.�

�After� the� serial� loopback� status� in� the� interface� changes,� the� DataChk� Status� field�

�may� show� unsynced� for� some� channels� due� to� the� asynchronous� nature� of� the� serial�

�loopback� signal.� The� Data� Patrst� should� be� asserted� in� this� case� to� synchronize� the�

�error� checker� with� the� transmitted� data.�

�Data� Patterns�

�The� application� supports� high-� and� low-frequency� patterns� for� PRBS15i,� PRBS7,�

�PRBS23� and� PRBS31.� No� synchronization� patterns� are� sent� prior� to� sending� the� PRBS�

�pattern.� Therefore,� you� can� use� a� third� party� receiver� to� recognize� the� PRBS� data.�

�Data� verifiers� are� not� available� for� the� high� frequency� (1010..)� and� low� frequency� (5’1s�

�and� 5’0s)� patterns.�

�Transceiver� Signal� Integrity� Development� Kit,�

�Stratix� IV� GT� Edition� User� Guide�

�January� 2012� Altera� Corporation�

�发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

DLP-2232H

MODULE USB ADAPTER FOR FT2232H

DLP-2232ML-G

MODULE USB ADAPTR FOR FT2232D LP

DLP-2232MSPF

MODULE USB ADAPTER WITH MCU

DLP-CB-DLPC200-10R

BOARD CONTROLLER FOR DLP

DLP-D-G

MODULE USB SECURITY DONGLE

DLP-HS-FPGA2

MODULE USB ADAPTER FOR FT2232H

DLP-IOR4

MODULE LATCHING-RELAY 4-CH

DLP-TEMP-G

MODULE DATA-ACQUISITION 3-CH

相关代理商/技术参数

DK-SI-4SGX230N

功能描述:可编程逻辑 IC 开发工具 FPGA Development Kit For EP4SGX230

RoHS:否 制造商:Altera Corporation 产品:Development Kits 类型:FPGA 工具用于评估:5CEFA7F3 接口类型: 工作电源电压:

DK-SI-5SGTMC7/ES

功能描述:可编程逻辑 IC 开发工具 FPGA Starter Kit For Stratix V 5SGTMC7 ES

RoHS:否 制造商:Altera Corporation 产品:Development Kits 类型:FPGA 工具用于评估:5CEFA7F3 接口类型: 工作电源电压:

DK-SI-5SGTMC7N

功能描述:可编程逻辑 IC 开发工具 FPGA Starter Kit For Stratix V 5SGTMC7

RoHS:否 制造商:Altera Corporation 产品:Development Kits 类型:FPGA 工具用于评估:5CEFA7F3 接口类型: 工作电源电压:

DK-SI-5SGXEA7/ES

功能描述:可编程逻辑 IC 开发工具 FPGA Starter Kit For Stratix V 5SGXEA7 ES

RoHS:否 制造商:Altera Corporation 产品:Development Kits 类型:FPGA 工具用于评估:5CEFA7F3 接口类型: 工作电源电压:

DK-SI-5SGXEA7N

功能描述:可编程逻辑 IC 开发工具 FPGA Starter Kit For Stratix V 5SGXEA7

RoHS:否 制造商:Altera Corporation 产品:Development Kits 类型:FPGA 工具用于评估:5CEFA7F3 接口类型: 工作电源电压:

DK-SL900A

制造商:ams 功能描述:Development kit for SL900A EPC Gen2 Sensory Tag IC

DK-SOC-10AS066S-A

功能描述:Arria 10 GX FPGA Evaluation Board 制造商:altera 系列:Arria 10 GX 零件状态:有效 类型:FPGA 配套使用产品/相关产品:Arria? 10 GX 内容:板 标准包装:1

DKSPS-001

制造商:Cooper Bussmann 功能描述:SMALL PARTITION PLATE DP25, DP35, DP45 A - Bulk 制造商:COOPER BUSSMANN 功能描述:SMALL PARTITION PLATE DP25, DP35, DP45 A